Lam 리서치에서 SEMulator3D 소프트웨어를 사용해 3D DRAM 아키텍처를 시뮬레이션했습니다. 스케일링/레이어 적층/캐패시터와 트랜지스터 축소, 셀 사이의 연결/TSV 구축 등의 문제를 이 시뮬레이션으로 검증하는 것이 목적입니다.

DRAM 셀은 종횡비가 매우 높기에 2D DRAM을 옆으로 눕혀서 쌓는 것이 불가능합니다. 그래서 지금 이상의 측면 에칭이 필요합니다. 하지만 DRAM의 구조를 잘 이해한다면 다른 방식으로 해결할 수 있겠지요.

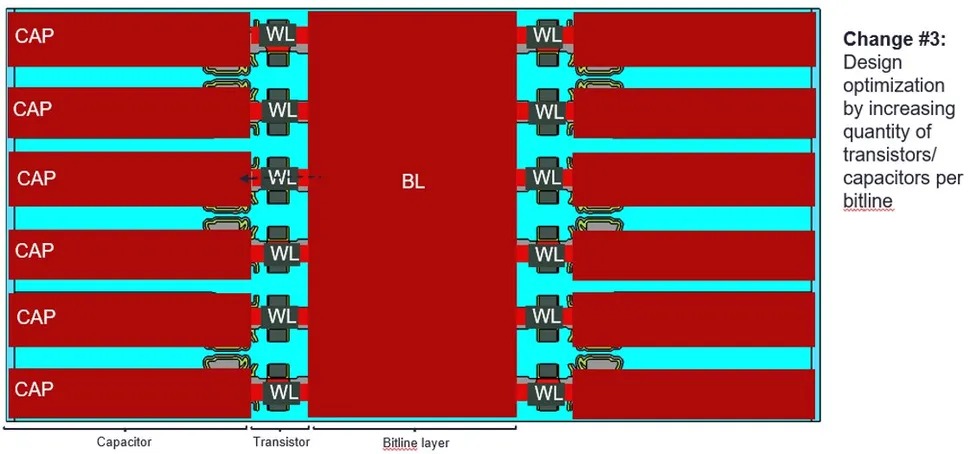

DRAM은 전류를 주입하는 전도성 구조인 비트라인, 비트라인의 전류 출력을 받아 전류가 회로로 들어갈 수 있는지 제어하는 게이트 역할의 트랜지스터, 비트라인과 트랜지스터의 전류가 0이나 1로 저장되는 캐패시터까지 세가지 구성 요소가 필요합니다.

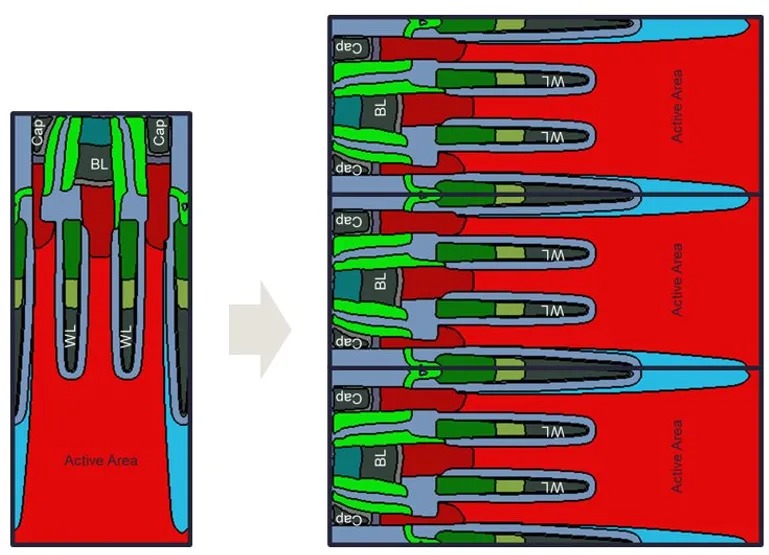

이 구조에선 비트라인을 트랜지스터의 반대편으롬 옮겼습니다. 캐패시터가 비트라인을 둘러싸지 않기에 비트라인에 더 많은 트랜지스터를 연결할 수 있어 칩 밀도가 향상됩니다.

또 저장 밀도를 최대화하기 위해 GAA를 비롯한 최신 디자인을 도입했습니다. 그리고 낸드 플래시 메모리 생산에서 썻던 공정으로 새로운 DRAM 셀 디자인 레이어를 적층했습니다.

현 새대 낸드 플래시 메모리가 232단 적층에 달하지만 이번 연구에서는 28단 적층까지 가능합니다. 그래도 아키택처 개선과 추가 레이어를 통해 2노드에 달하는 밀도 향상이 가능하다고 보고 있습니다.

https://newsroom.lamresearch.com/3D-DRAM-architecture-proposal