컴퓨터/노트북/인터넷

IT 컴퓨터 기기를 좋아하는 사람들의 모임방

Imec Reveals Sub-1nm Transistor Roadmap, 3D-Stacked CMOS 2.0 Plans

반도체 연구 회사인 Imec가 1nm 이하 실리콘/트랜지스터 로드맵을 공유했습니다. 여러 반도체 업체들과 함께 개발할 공정의 로드맵을 대략적으로 제시하고 있는데요.

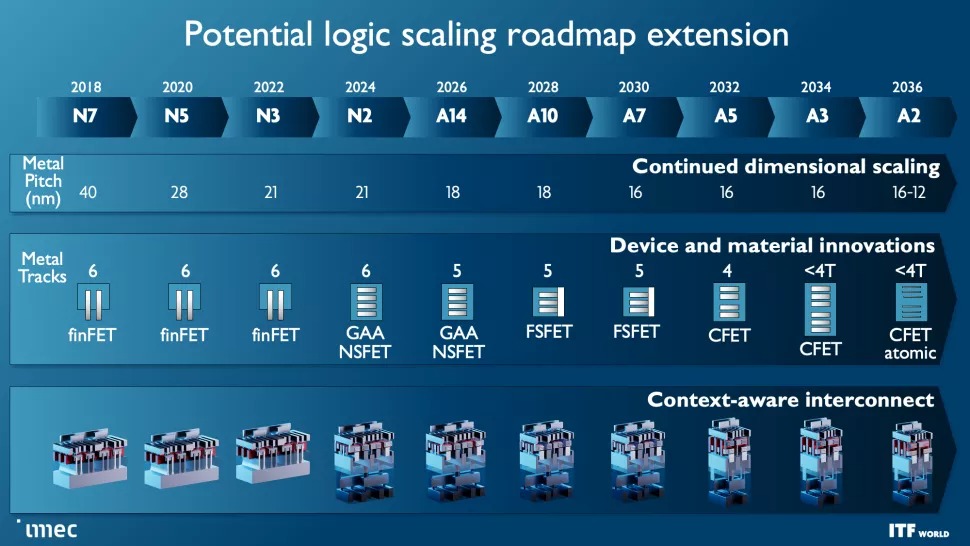

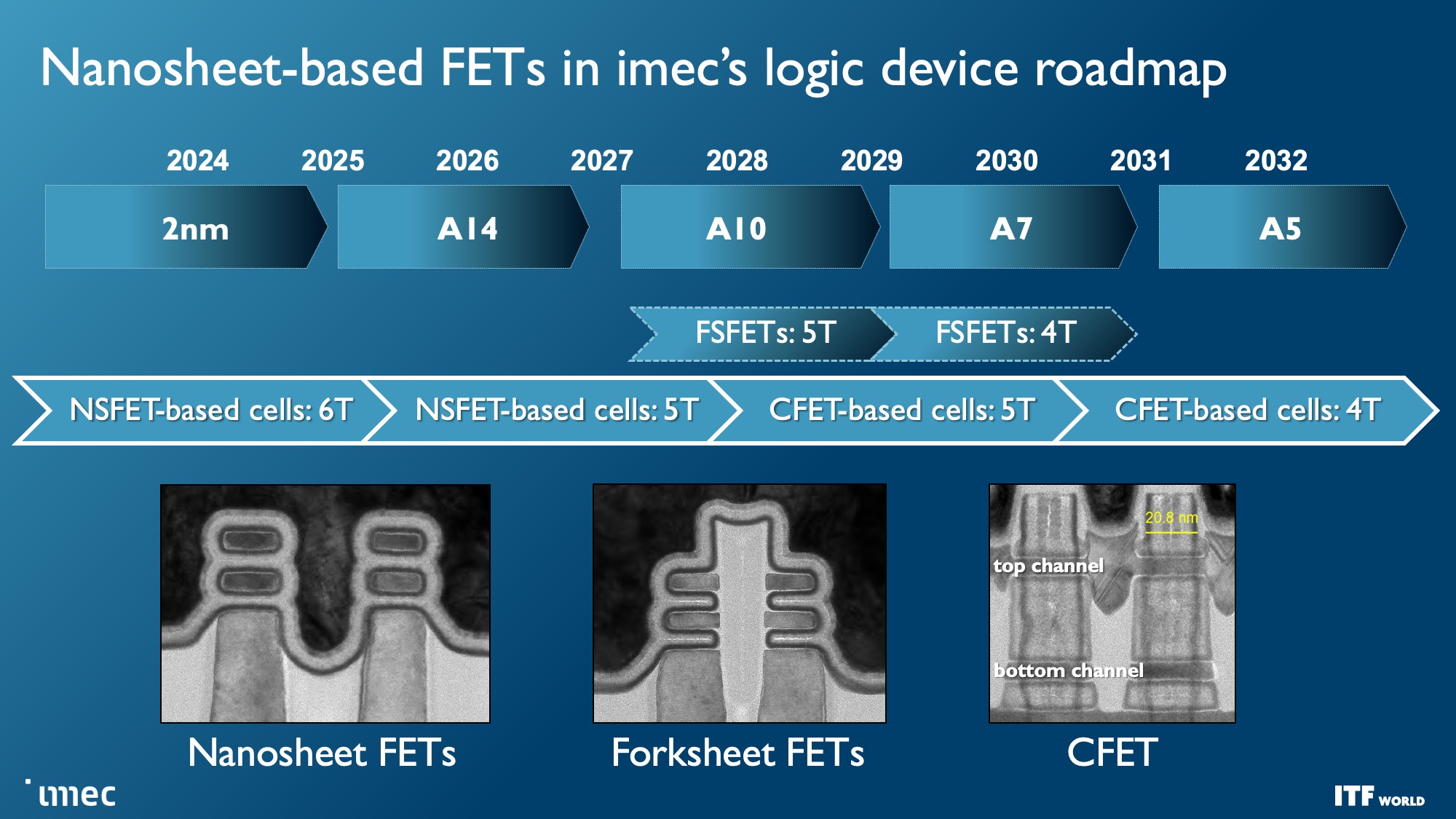

10옹스트롱은 1nm니까 A7부터는 1nm 이하의 노드를 가리킵니다. FinFET는 3nm까지 계속되지만 2024년부터 GAA 나노시트로 바뀌며, 2nm와 0.7nm에서 포크시트를 사용합니다. 또 A5와 A2에서는 CFET와 아톰 채널 같은 획기적인 설계가 포함됩니다.

결국은 이게 다 돈입니다. 신형 공정은 갈수록 비싸기에 큰 다이를 통째로 비싼 새 공정으로 만드는 건 수지타산이 맞지 않습니다. 더 큰 다이를 만들기 위해서도 있지만, 칩을 나눠 구형 공정을 쓸 수 있는 부분은 빼서 가격을 낮추는 것 역시 칩렛의 목적입니다.

칩렛은 칩을 나눈다고 해서 되는 게 아니라 전력 공급, I/O, 캐시 등의 기능 유닛을 분리하고 각각의 유닛에서 필요한 성능에 맞춰서 최적화를 해야 합니다. 여기에선 전력 공급을 TSV를 통해 트랜지스터 뒷면으로 빼서 데이터 연결과 전력 공급을 분리해 성능을 높이는 방법을 설명하고 있습니다.

또 3D 패키징에 대한 내용도 있습니다. 캐시는 신형 공정을 써도 크기가 많이 줄어들지 않습니다. 이걸 별도의 다이로 빼서 크게 만들고 그 위에 신형 공정으로 만든 코어를 얹으면 용량을 늘리고 레이턴시도 줄일 수 있습니다.

https://www.tomshardware.com/news/imec-reveals-sub-1nm-transistor-roadmap-3d-stacked-cmos-20-plans