단축키

Prev이전 문서

Next다음 문서

단축키

Prev이전 문서

Next다음 문서

퀄컴은 스냅드래곤 8 Gen2를 위해 TSMC와 공동 개발한 4nm FinFET 공정으ㅡㄹ VLSI에서 설명했습니다.

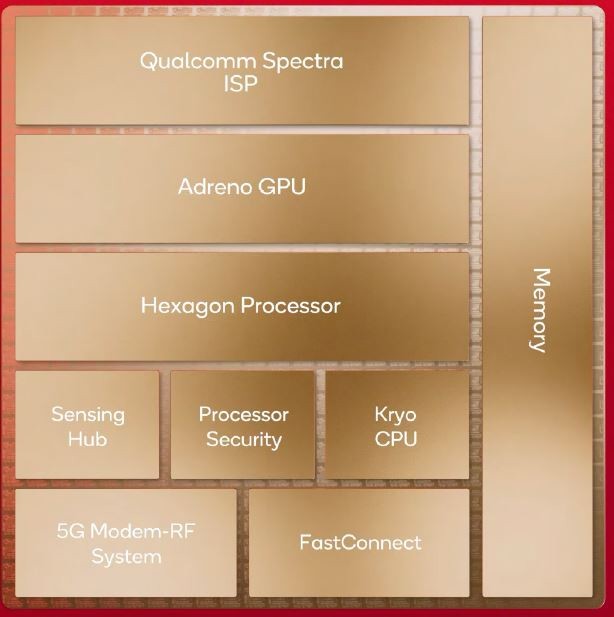

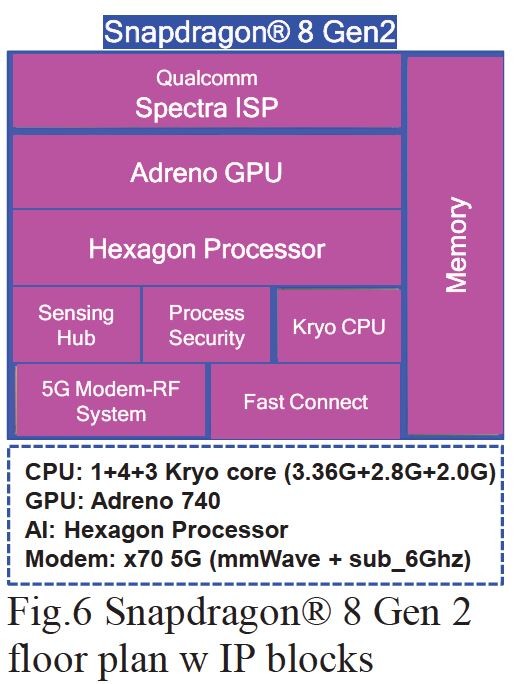

스냅드래곤 8 gen2는 퀄컴이 2022년 11월에 발표한 5G용 SoC로 8코어 CPU, GPU, DSP, ISP, 5G 모뎀, 보안 코어, 센서 허브 코어 등이 포함됩니다.

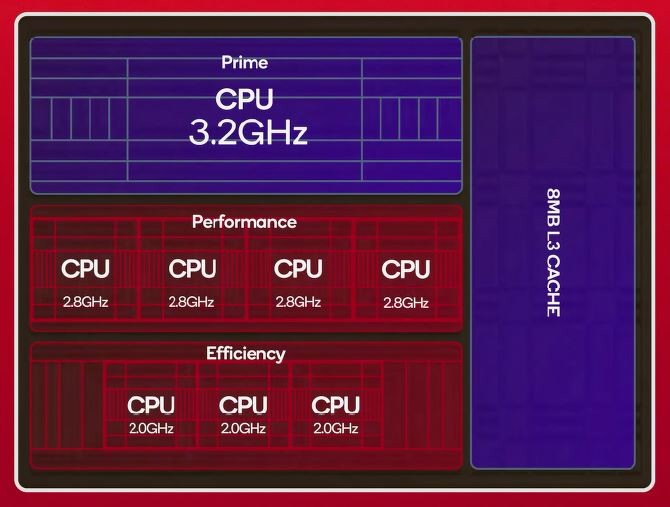

CPU는 최고 클럭 3.2GHz인 프라임 코어(Cortex-X3), 2.8GHz인 퍼포먼스 코어(cortex-A715 x2, Cortex-A710 x2), 2GHz의 효율 코어(Cortex-A510 x3)으로 구성되며 8MB L3 캐시를 공유합니다.

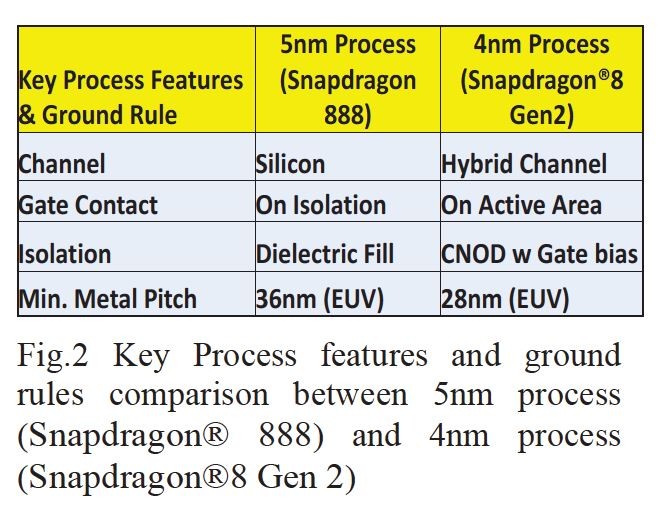

4nm 공저으이 특징은 기존 스냅드래곤 888에서 쓴 5nm 공정과 비교했습니다. 모두 FinFET 트랜지스터를 사용하지만 많은 부분이 다릅니다. 5nm는 실리콘 채널을, 4nm는 하이브리드(SiGe) 채널을 트랜지스터 채널에 사용했습니다. 덕분에 MOS FET의 속도가 빨라집니다.

게이트 컨택트는 5nm에서 소자와 분리시키는 방법을 유지했으나 4nm는 액티브 에어리어에 컨텍트를 만들어 트랜지스터 소형화에 기여했습니다. 표준 셀의 분리는 5nm가 절연막을 썼지만 4nm는 CNOD(Continuous Diffusion)이라는 더미 게이트 바이어스를 썼습니다. 확산 영역을 분리하지 않기에 표준 셀의 크기가 줄어듭니다.

노광은 모두 EUV입니다. 5nm는 최소 배선 피치가 36nm이며 EUV 싱글 패터닝입니다. 하지만 4nm는 27.4nm로 피치가 줄었고 EUV 더블 패터닝을 썼습니다. 그래서 게이트 피치x최소 배선 피치의 크기는 25% 가량 줄었고 SRAM의 크기는 20% 줄었습니다.

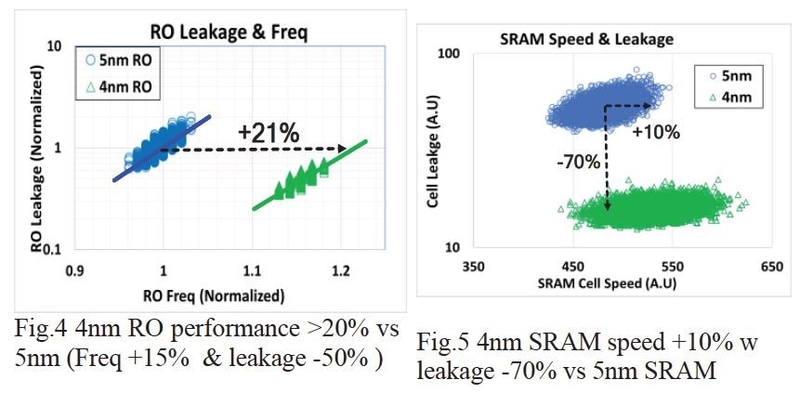

기본 회로인 링 발진기의 SRAM 셀의 성능을 비교한 것입니다. 4nm에서는 링 발진기의 클럭이 15% 오르고 누설 전류는 절반이 됐습니다. SRAM 셀은 클럭이 10% 오르고 누설 전류가 1/3이 됐습니다.

또 CPU 성능은 25%, GPU 성능은 100% 오르고 배터리 사용 시간은 22% 늘어납니다. 4nm의 전압 편차는 5nm의 절반으로, 누설 전류 편차는 15% 줄었습니다.

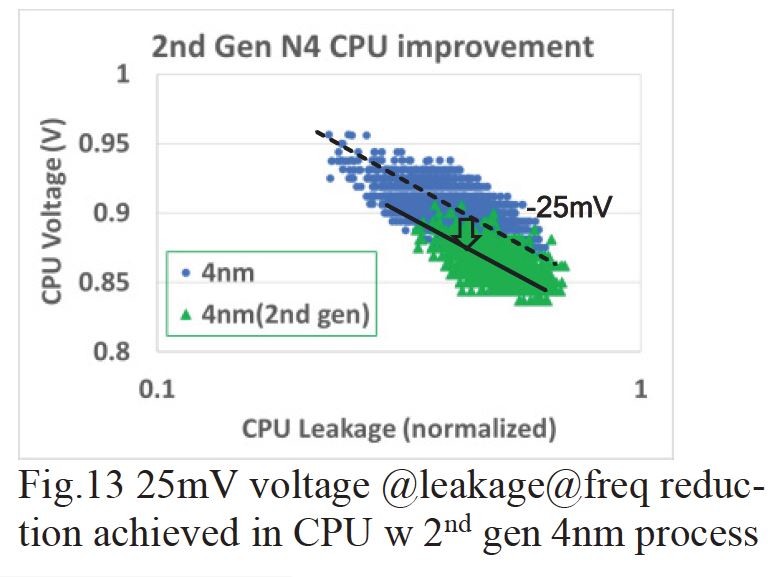

또 2세대 4nm FinFET 공정의 프로토타입도 소개했습니다. 올해 가을에 나올 스냅드래곤 8 Gen3에서 이걸 쓸 것으로 보입니다. 여기에선 링 발진기의 클럭이 4% 오르고 배선 공정의 저항을 줄였습니다. V0은 21%, V1은 23% 줄어듭니다.

누설 전류와 클럭을 똑같이 유지한다는 조건 하에 동작 전압은 25mW 줄어듭니다.

https://pc.watch.impress.co.jp/docs/news/1511640.html