컴퓨터/노트북/인터넷

IT 컴퓨터 기기를 좋아하는 사람들의 모임방

단축키

Prev이전 문서

Next다음 문서

단축키

Prev이전 문서

Next다음 문서

TSMC가 6배 크기의 슈퍼 캐리어 인터포저를 준비하고 있습니다.

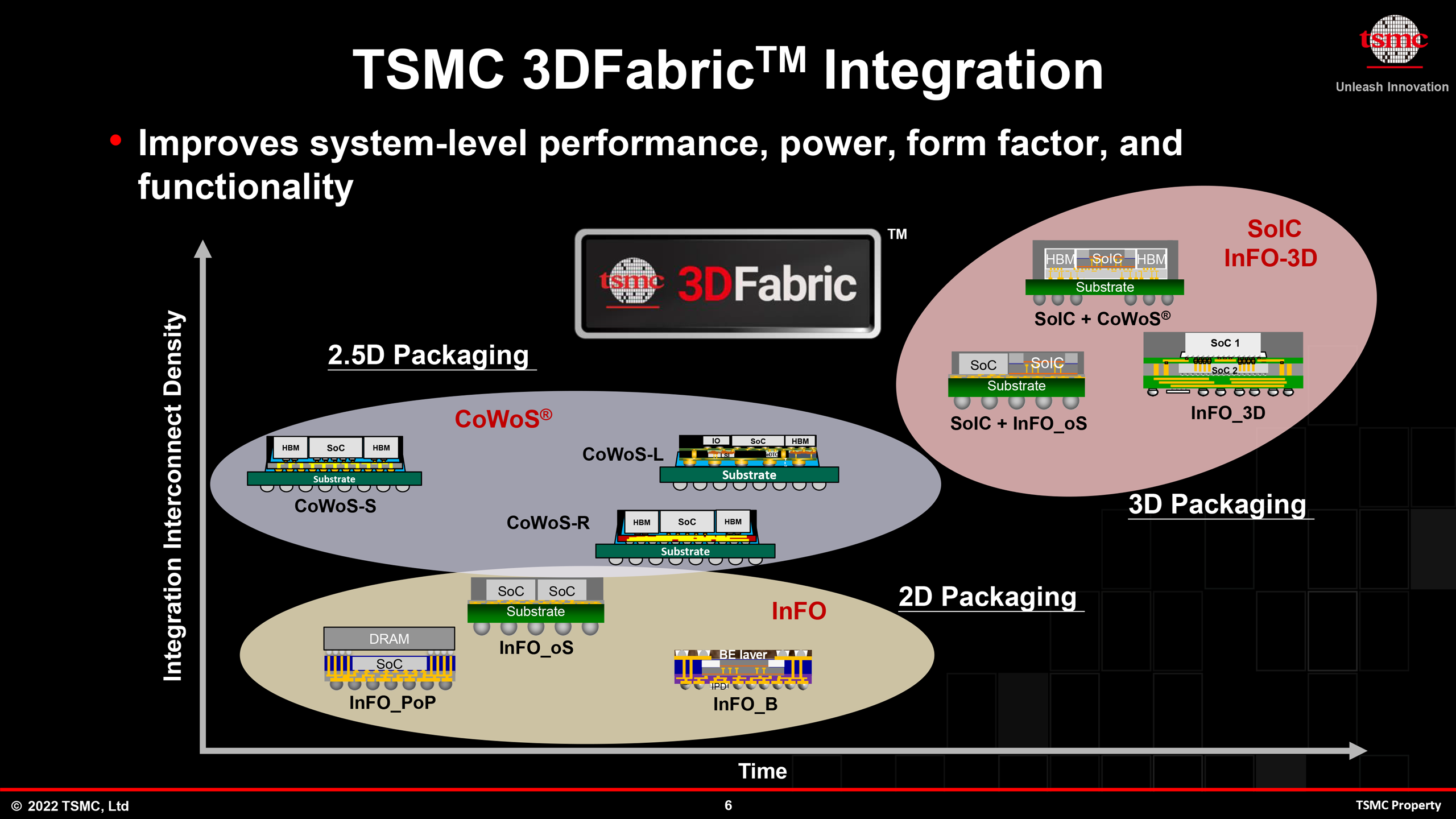

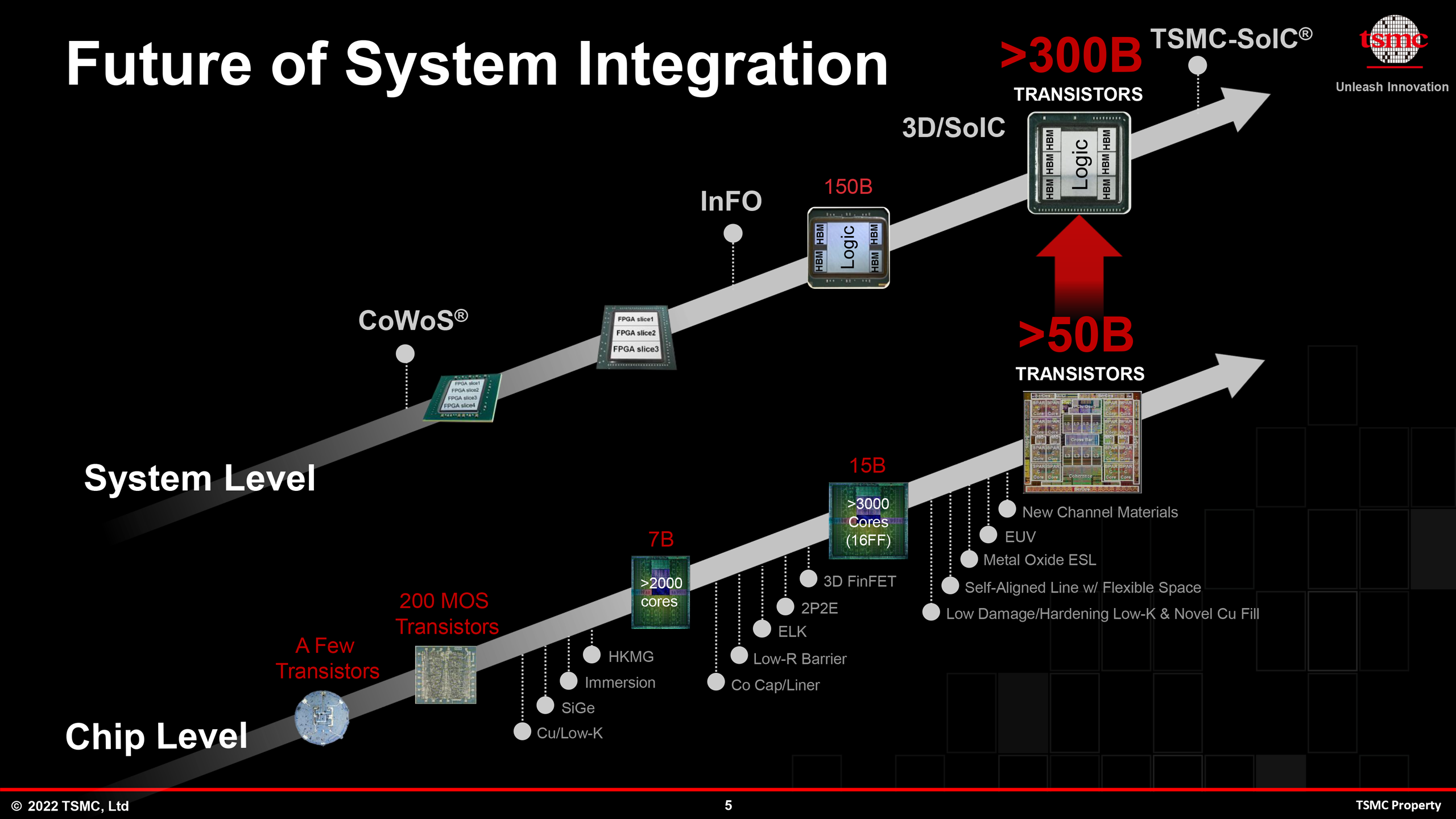

현재 반도체 업계에선 갈수록 더 높은 성능의 칩을 필요로 하고 있으나, 기존 공정에서 만들 수 있는 칩의 크기에는 한계가 있습니다. 그래서 여러 칩렛을 함께 패키징하는 방법이 등장했으며 TSMC는 CoWoS 패키징을 도입한 바 있습니다.

TSMC의 차세대 CoWoS 공정은 인터포저의 크기를 기존의 3.3배에서 6배까지 키워 더 많은 칩렛을 배치할 수 있게 해줍니다. 이론적인 EUV 레티클 한계는 858mm2(26mm x 33mm)이니까 6배로 늘어나면 5148mm2의 SiP 패키징이 가능해집니다.

더 많은 컴퓨팅 칩렛 외에도 12스택 HBM3 같은 걸 집어 넣을 수 있습니다. 이 경우 9.8TB/s의 대역폭을 지닌 메모리 인터페이스가 나옵니다.

물론 이렇게 큰 SiP 패키징은 매우 비쌀 수밖에 없습니다. 현재 NVIDIA H100 가속기만 하더라도 3만 달러를 쓰는데, 차세대 CoWoS는 더 비쌀 겁니다.

HPC를 위한 N4X 공정의 정보도 공개됐습니다. N4X는 N5(5nm) 급 공정이지만 오버드라이브 모드에서 1.2V의 높은 전압으로 작동합니다.

https://www.anandtech.com/show/18875/tsmc-details-n4x-extreme-performance-at-minimum-leakage

TSMC는 성능과 효율을 높이기 위해 크게 3가지 부분에서 설계를 개선했습니다. 처리 속도와 구동 전류를 높이는 트랜지스터의 개선, 고밀도 MiM 캐패시터를 통합해 높은 부하에서 안정적인 전력 공급, 후공정 메탈 스택으로 더 많은 전력 공급이 그것입니다.

N4X uLVT 오버드라이브는 N4P eLVT와 비교해서 같은 속도에서 전력 사용량이 21% 낮거나, 같은 전력에서 속도가 6% 높습니다. N4X는 N4나 N4P에서 상당한 성능 향상을 이루었지만 SRAM, I/O, IP 등이 같기에 N4X로 마이그레이션하기 쉽습니다.

N4X는 내년에 생산될 예정입니다. 2030년에는 N4X 공정의 40%를 HPC가, 30%를 스마트폰, 자동차가 15%를 차지합니다.