컴퓨터/노트북/인터넷

IT 컴퓨터 기기를 좋아하는 사람들의 모임방

단축키

Prev이전 문서

Next다음 문서

단축키

Prev이전 문서

Next다음 문서

엔비디아 CEO 젠슨 황은 최근 몇 년간 공개석상에서 "무어의 법칙은 죽었다"고 밝혔습니다. Intel과 AMD 경영진은 서로 다른 견해를 갖고 있지만 최근 Google이 발표한 보고서는 다시 한번 Huang Renxun의 견해를 뒷받침합니다.

무어의 법칙은 인텔 창립자 중 한 명인 고든 무어의 경험으로, 핵심 내용은 집적 회로에 수용할 수 있는 트랜지스터 수가 18~24개월마다 약 두 배로 늘어난다는 것입니다. 즉, 프로세서 성능은 대략 2년마다 두 배로 증가하는 반면 가격은 이전보다 절반으로 떨어집니다.

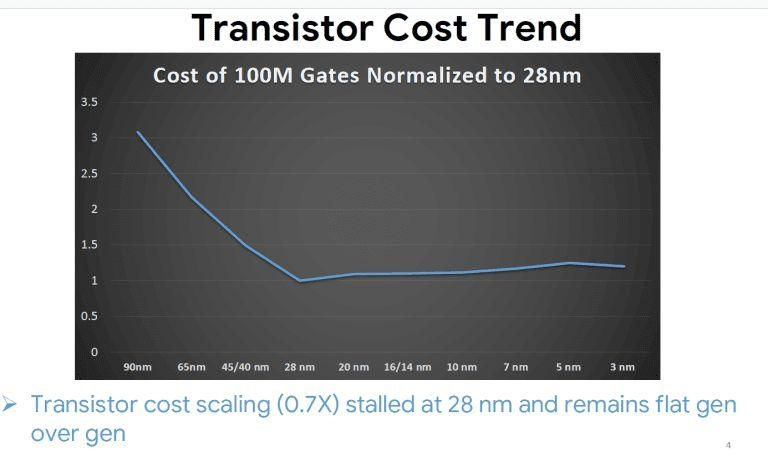

1억 개의 게이트 트랜지스터 비용은 2014년 28nm 이후 정체되어 감소하지 않았습니다.

3차원 반도체 통합 기업 MonolithIC 3D의 CEO인 Zvi Or-Bach는 이르면 2014년 초에 분석 보고서를 제출했는데, 이는 트랜지스터당 비용이 28나노미터에서 더 이상 떨어지지 않았다는 것을 보여줍니다.

Google의 Milind Shah는 IEDM 2023의 단기 과정(SC1.6)에서 이 진술을 확인했습니다. 그는 TSMC가 2012년 28나노 평면 공정 기술을 양산한 이후 게이트 단위 트랜지스터 1억개 가격이 오히려 올랐을 뿐, 저렴해지지 않았다고 지적했다.

위 그래프를 보면 게이트 트랜지스터 1억개 가격이 떨어지지 않았음을 알 수 있다

Google 연구 결과에 따르면 "트랜지스터 비용 증가(0.7배)는 28nm에서 정체되었으며 세대 간 변동이 없었습니다."

업계에서는 새로운 노드의 단위 트랜지스터 비용에 대한 수익 감소에 대해 오랫동안 우려해 왔습니다. 7nm, 5nm, 3nm의 지속적인 발전 속에서 칩 제조 공정 기술은 수억 달러(ASML Twinscan NXE 리소그래피 기계의 비용은 US$2억)에 달하는 보다 복잡한 Fab 도구를 필요로 하며, 최첨단 비용을 팹 규모는 200억~300억 달러 수준에 이른다.

그러나 지난 몇 년 동안 칩 제조가 점점 더 복잡해지고 비용이 많이 드는 반면, 더 큰 그림을 보는 것이 중요합니다.

실제로 업계 박람회 IEDM에서 Google의 Milind Shah가 발표한 차트에 따르면 28nm에서 1억 개의 트랜지스터 비용은 실제로 변동이 없거나 심지어 증가하고 있습니다.

프로세스 발전의 원동력은 무엇입니까?

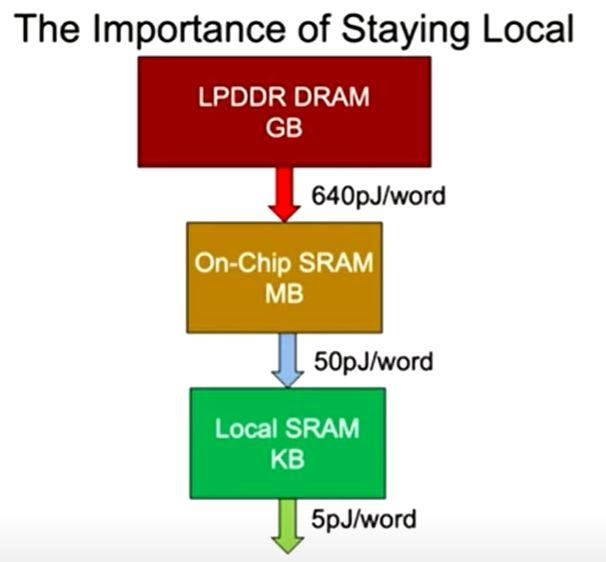

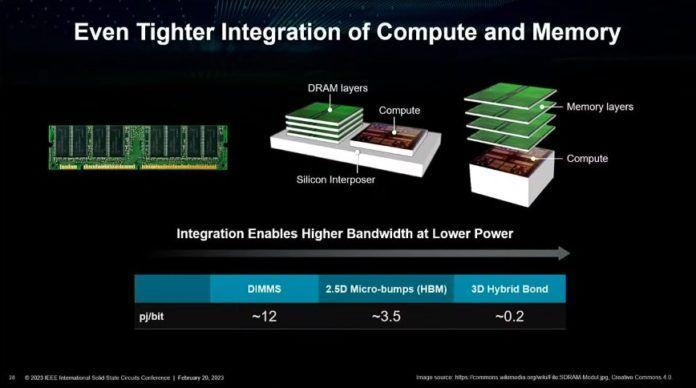

비용 절감이 정체되는 상황에서도 업계에서는 놀라운 1nm 노드 도달을 목표로 계속해서 크기가 작아지는 트랜지스터를 추진하고 있는 이유는 무엇일까요? 대답은 시스템 수준의 이점에 있습니다. NVIDIA의 수석 과학자인 Bill Dally가 그린 이 차트는 이 점을 보여줍니다.

이미지 출처: Bill Dally, Berkeley EECS, 2022년 11월 30일

이는 결과적으로 CPU 및 GPU와 같은 주요 컴퓨팅 장치가 입자 크기에 도달하거나 초과하는 추세를 주도합니다. 더 작은 노드를 추구하면 칩의 구성 요소가 더욱 긴밀하게 통합되어 성능과 효율성이 더욱 향상됩니다.

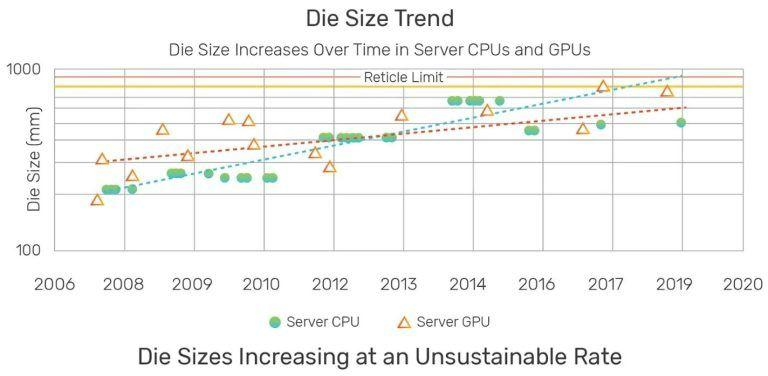

다음 그림은 다이(다이/다이) 크기 추세를 보여줍니다.

출처: AMD

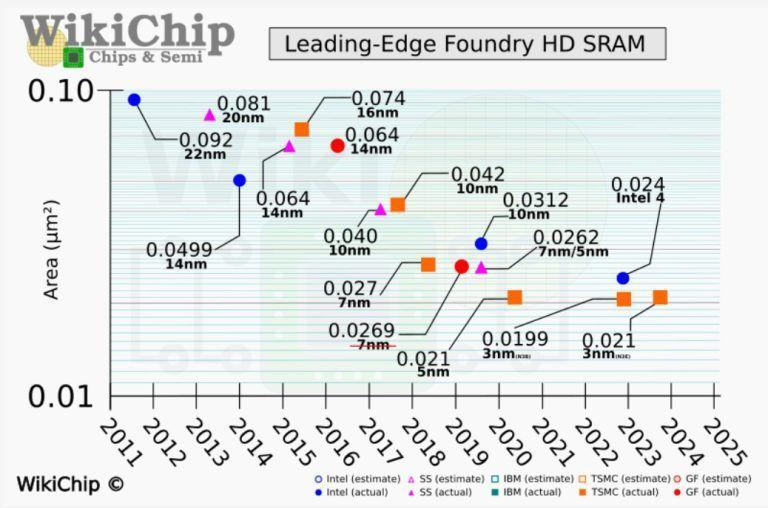

불행하게도 로직과 메모리(DRAM, NAND)는 매우 다른 프로세스를 사용하여 제조됩니다. 따라서 서로 다른 웨이퍼에서 생산되며 스케일링을 통해 통합될 수 없습니다. 설상가상으로 SRAM 비트 셀의 스케일링이 5나노미터 노드에서 중단되었습니다.

이미지 출처: WikiChip

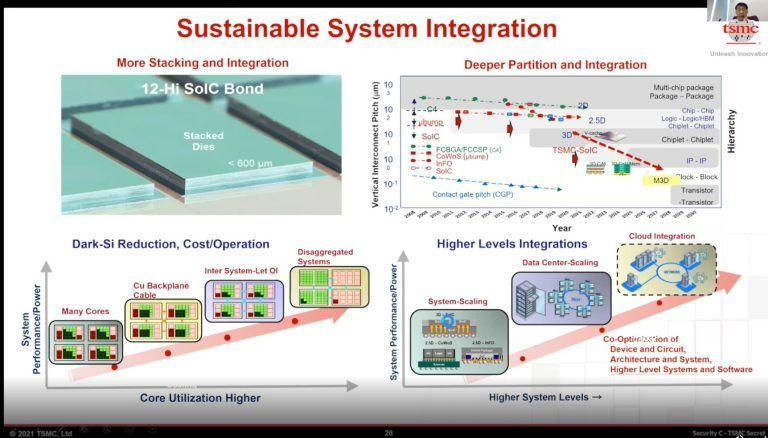

AMD와 TSMC는 모두 이러한 추세를 이해하고 지난 몇 년 동안 하이브리드 본딩 기술을 적용하여 컴퓨팅 성능을 더욱 향상시킨 것으로 보입니다.

출처: 리사 수 박사

출처: TSMC

Chiplet 솔루션이 인기를 끌고 있습니다.

칩렛(Chiplet)은 영어로 사전 제작되어 특정 기능을 갖고 결합, 통합이 가능한 다이(Die)를 말한다.

단일 실리콘 조각으로 만든 모놀리식 설계를 생산하기 위해 최첨단 노드를 사용하는 것보다 비용과 성능을 최적화하기 위해 특정 설계를 칩렛으로 분리하는 것이 공급업체에게 더 매력적입니다.

클라이언트 도메인

클라이언트 컴퓨팅 분야에서 분리 설계의 가장 대표적인 예는 AMD의 Ryzen 데스크톱 CPU와 Intel의 Meteor Lake 노트북 CPU로, 서로 다른 공장에서 서로 다른 프로세스를 사용하여 제조됩니다.

데이터센터 분야

데이터센터 분야에서는 AMD의 EPYC 데이터센터 CPU도 성공적인 사례다. AMD 및 Intel과 같은 수십억 달러 규모의 기업은 설계 옵션을 신중하게 평가한 다음 원하는 대로 최고의 기술을 사용하여 제품을 구축할 수 있습니다.

소규모 제조업체의 경우 상황이 그렇게 간단하지 않을 수 있습니다.

멀티 코어 디자인

첫째, 다중 칩렛 설계는 모놀리식 설계보다 더 많은 전력을 소비하는 경향이 있으므로 모바일 장치에 가장 적합한 선택이 아닙니다.

멀티 칩렛 설계는 어려운 엔지니어링 작업이며, MonolithIC 3D와 같은 회사가 멀티 칩 통합 서비스(결국 Intel의 Foveros 또는 TSMC의 CoWoS와 같은 고급 패키징 기술 사용)를 제공하지만 서비스 비용은 저렴하지 않습니다.

셋째, 고급 패키징 기술의 비용이 높으며 일부 제조업체가 기꺼이 비용을 지불하더라도 TSMC의 CoWoS 패키징 생산 능력이 부족하고 요구 사항을 충족할 여유 용량이 분명히 없습니다.